|

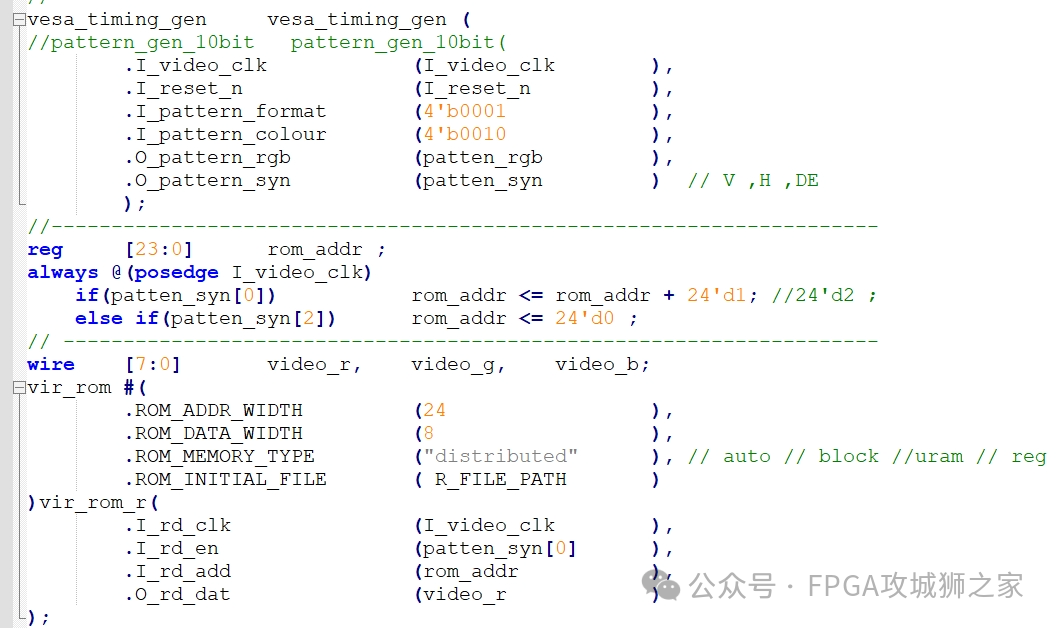

竞技宝官网app·FPGA图像处理—VESA标准与流介绍器就完成了。有人会说,这个东西,不就是xilinx官方的IP VTC 嘛,干嘛要重复造轮子。嘿嘿,那是因为,一,我们在做图像处理的时候要尽量的避免使用viv,因为它实在是太墨迹了。二,如果是1080p以上的分辨率,比如4k,8k,的视频流,它在FPGA里面是双点,四点模式的,VTC没有这个功能,这个就要靠自己去实现了。 这是一张黑白图导入到matlab中,然后再保存到txt中的程序。然后在FPGA中将txt导入到rom,利用VESA视频流同步信号产生器,虚拟一条视频输入到代码中。

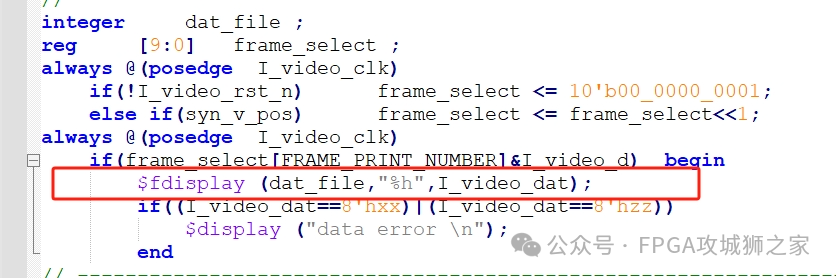

vir_rom 就是一个虚拟的rom。利用VESA视频流同步信号产生rom读地址,从而把rom中的图像数据导出来。 仿真的下半场,就是将视频流存入到文件中,这里需要写一个视频保存文件,选择其中一帧保存下来。此时modelsim会产生一个txt文件,保存我们所需要的数据。

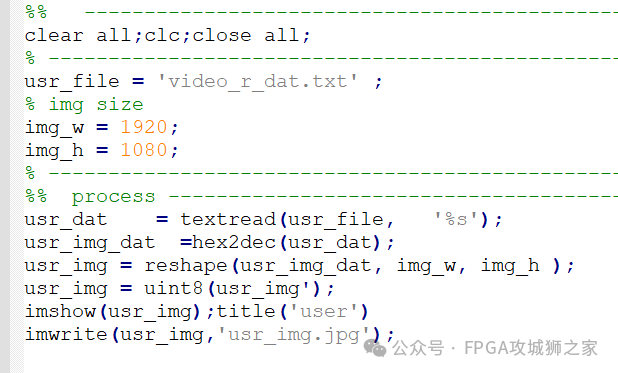

当我们拿到了modelsim里面的仿真视频流一帧的文件txt,直接读入到matlab里面去就好了。几行代码就完成了华丽的转换。

自此,测试图产生器就完成了。既可以放到可综合项目中,也可以放到仿真工程中使用。自此,这个结构图里面的内容就完成了。 竞技宝官网app |